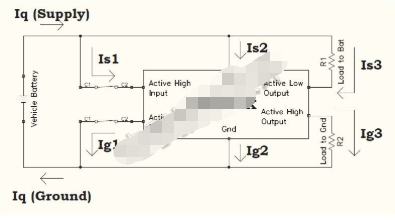

随着汽车电子控制器在汽车里的数量越来越多,对于汽车电子控制器静态电流的要求也在不断增高。如何降低汽车电子控制器的静态电流,也成为系统硬件设计中的一个难点和挑战。本文希望就此主题做个有限范围的讨论,阐述如何从硬件设计角度来降低静态电流。图1给出了典型的汽车电子模块示意图,由于这个主题所涉及的范围比较多,下面我们只讨论以下三种情况下静态电流的处理:

(1)有源低有效输入(Active Low Input);

(2)有源低有效输出(AcTIve Low Output);

(3)对电源的处理。

在汽车电子模块设计中如何降低静态电流,从哪几方面进行处理

(1)有源低有效输入

为有源低有效输入的电路图。图中V+ = 12.8V,S1为“开”的状态,微处理器供电电压为5.0V。

在汽车电子模块设计中如何降低静态电流,从哪几方面进行处理

如果按照IQ = 12.8V/(R1 + R2 + R3) = 86mA来计算这个电路的漏电流,那就可能错了!正确的计算是:绝大多数微处理器的I/O口都会有一个用于输入保护的钳位二极管(Clamp Diode),例如图3中的D2。钳位二极管D2会连接到微处理器的供电电源,因此实际用来分析的电路应该是如图3所示。

在汽车电子模块设计中如何降低静态电流,从哪几方面进行处理

因此,IQ =[V + (-5.6V)]/(R1 + R2) = 148(mA)。

这个计算结果和未考虑钳位二极管的计算结果有62mA的差别(148mA - 86mA = 62mA),对于有多个有源低有效输入的控制器来说(比如车身控制器BCM),还是不能忽视的。

为了更好地验证控制器中的静态电流,还需要仔细验证如下的每一项:

- 如果可以的话,关掉上拉电阻,因为它会提供电流到地的路径;

- 哪个输入引脚是高有效、低有效、不活动状态、开路状态;

- 是否有任何外部负载或开关与输入或输出并联,它们的状态是什么。

(2)有源低有效输出

对于有源低有效输出电路,又该如何考虑连接负载后在模块中的漏电流呢?

对于双极性晶体管(BJT)集电极开路(OC)的应用(图4),要特别注意温度变化对漏电流的影响,特别是ICEO对晶体管BJT的影响。ICEO是由少数载流子漂移运动形成的,它与环境温度关系很大,ICEO随温度上升会急剧增加。温度每上升10℃,ICEO将增加一倍。用MOSFET作为低边输出或者高边输出则好很多,因为MOSFET本身的源漏电流就很小,且MOSFET对温度的变化不敏感。

在有源低有效输出情况下,考虑优化静态电流的一些对策包括:

- 考虑用MOSFET或者达林顿管来替代双极性晶体管;

- 哪些输出为开、关、外部接地或供电。

为了更加地分析控制器的静态电流,可以用表格把每个单元电路“贡献”的静态电流全部列出这样可以一目了然,对控制器的静态电流的分布熟谙于心。

在汽车电子模块设计中如何降低静态电流,从哪几方面进行处理

从中可以看出,规格书(Spec)要求静态电流是2.0mA,分析出来的结果是2.46mA,差电路分析情况下是2.934mA。总的静态电流超过了规格书的要求,接下来的设计任务就是如何进一步减少每个单元电路的静态电流来满足规格书的要求。

(3)对电源的处理

用处理器的I/O控制在系统关电(点火开关“关”)时把不用的电源关掉是个不错的办法。如图6所示,VBATT1经过一个受处理器I/O控制的开关变成VSWBAT——图6中Q24的基极B用处理器的一个I/O来控制,置“高”时VSWBAT打开,置”低”时VSWBAT关闭。这样可以在需要有VBATT1供电时再接通它。

在汽车电子模块设计中如何降低静态电流,从哪几方面进行处理

以下为对电源处理的一些设计建议:

- 考虑使用更低静态电源功耗的IC;

- 对于开关电路,选择NPN/PNP配置,以便所有设备都能在静态状态下关闭(不需要一个晶体管打开,那就用另一个晶体管来保持它关闭);

- 识别电流流过的每个供电(或接地)路径,仅包括电流通过模块,而不是绕过模块的电流;

上面初步讨论了对于降低静态电路的一些建议和经验。对于汽车电子的整体设计来说,这些还是不够的,还需要在系统的层面来做更深入的研究,例如以下的一些建议。

更进一步考虑用于减少系统静态电流的一些建议:

- 尽可能降低开关时钟速度(尤其是微处理器的振荡器);

- 使用具有可用中断或唤醒输入的微处理器,这些输入可以配置为允许微处理器“休眠”;

- 降低必须间歇性唤醒然后重新进入睡眠状态的电路的占空比;

- 对于必须在静态电流期间保持某些功能的模块,请考虑双时钟频率或双处理器架构;

- 同样,考虑使用允许主处理器在能够响应的情况下休眠的专用总线通信IC。

综上所述,静态电流的控制只有在设计的初期做好整体的架构拓扑设计、器件选型和优化、设计优化以及软件控制策略结合等工作,才可以将静态电流控制在规格书的范围以内。

Copyright © 2018-2020 PbootCMS All Rights Reserved. 粤ICP备18049383号

XML地图