设想一下:如果你驱车以每小时75英里的速度在高速公路上疾驰,一边驾驶着2006才购买的新车,一边欣赏着SteveMiller的GreatestHits乐曲。突然间,引擎管理系统或稳定控制系统失效。如果出现这一幕,您不仅仅可能会遭遇严重或可能是致命的车祸,而且车厂也可能被毁誉一旦,假设类似情况不止你一个的话。

随着汽车从纯机械设备向现代高度集成的线控驾驶汽车电子系统发展,设计工程现在面临越来越多的挑战。它们必须持续把复杂的电子设备添加到每一个后续车型年,与此同时,仍然要维持高标准的品质和可靠性,并满足严格的低成本和大批量生产的要求。

传统上,这些开发商一直采用微控制器(MCU)、ASIC和硕大的线束来实现和控制这些系统并扩展每一代汽车的性能。目前,这些技术已经逼近了它们的极限,并因复杂性呈指数增长而引发了对可靠性问题的关注。为了解决这些问题,许多设计工程师正在转向采用FPGA作为下一代汽车电子设计的灵活和低成本的解决方案。

太空射线引发的故障

为了确保现代汽车中各种系统的功能运转正常,必须对元器件提出可靠性数据的要求。虽然人们掌握元器件可靠性的大部分原理,但是,在选择可编程逻辑器件如FPGA的过程中,要把一些独特的问题纳入应该考虑的因素。

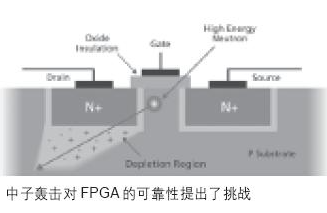

明确地说,技术决策人要预见到将影响可编程逻辑系统的故障源。虽然来自太空(宇宙射线)的中子轰击的概念听起来就像蹦出StarTrek的插曲,中子导致的错误现实上对许多类型的电子设备都有危害。

中子导致的固件错误(firmerror)已经从一件麻烦事变为重大问题。例如,如果中子导致基于SRAM(基于静态)的FPGA的(以下简称:SRAMFPGA)配置单元被扰乱,就可能导致功能丧失。如果出现这种情况,它就可能造成主系统失常。展望未来,这种问题将更为严重,因为将来的深亚微米制造工艺将持续为基于FPGA的汽车电子系统的设计工程师带来实实在在的挑战。

在集成电路内部由中子造成的单事件扰乱(SEU)可能在各种类型非易失性存储单元中都会出现。上述SRAMFPGA采用内部存储单元来保持FPGA的配置状态或(个性)。这些存储器单元面对更为严重的可靠性威胁。当内容被改变的时候,它被称为“软错误”,因为是数据错误,而功能不受影响。虽然该器件可以采用校正数据成功地重新写入,对SRAM数据和寄存器可以分别采用EDAC(错误检测和校正)或TMR(隧道磁阻)。软错误可能导致数据丢失或“系统出现意外故障”。

如果SRAMFPGA配置存储器单元受到破坏,那就称为“固件错误”,因为这些错误不易检测或校正并且本质上不是瞬时现象。一旦在FPGA中出现固件错误,必须采用初始配置对该器件进行重新载入。在一些情况下,必须重新上电以清除故障,然后,重新配置。

这些配置单元中,只要有一个遭遇中子导致的SEU,后果都是严重的。如果配置为被扰乱并改变状态,它可能会改变整个器件的功能,导致重大数据崩溃或向系统中的其它电路发送虚假的信号。在极端情况下,如果固件错误长期未被检测到其存在,那么,就能变成“硬故障(harderrors)”并对器件本身或包含该器件的系统造成破坏。这类问题的常见例子是:中子导致的稳故障把信号导向错误的路径,从而造成短路。

对于采用SRAMFPGA的、执行重要任务的汽车电子应用系统,中子导致的错误有着重要的影响。现有的检测技术,每隔一定间隔读回FPGA的配置,对防止系统内的错误毫无帮助。

此外,能够检测受破坏配置的读回电路本身就易于遭受SEU或破坏。进一步说,在检查汽车系统抗中子导致的错误中,随着易受影响的FPGA技术的广泛应用,人们要求把创新的质量 体系添加到AEC-Q100标准之中,以补充JEDEC标准89的不足。当前检测和校正FPGA固件错误的方案增加了系统设计的额外复杂性,并增加了电路板的大小和物料的成本,从而增加了发现中子导致的错误的“成本”。

中子导致的固件错误可能对整个系统按时间计算的故障(FIT)率影响很大。由于难以检测和几乎不可能诊断,软和稳故障可能引发维护和服务问题,从而有可能造成担保费用攀升。在三种主流FPGA技术—反熔丝、闪存和SRAM—之中,只有反熔丝和闪存免受抗中子导致的软错误和固件错误的影响。

实例:具有SRAMFPGA的汽车系统

本例分析一个安装在驾驶室内地板中的系统。中子射线密度以Denver计算,元素钴放置在5000英尺的高处,用SpaceRad4.5(一种广泛应用的辐射效应预测软件程序)工具测量。根据已出版的关于0.22umSRAMFPGA的辐射数据,每天每1百万门FPGA的预测扰乱率为1.05E-4。

如果供应商在乘员传感器和气袋控制模块中部署1百万门SRAMFPGA,把每天每1百万门器件为1.054E-4的扰乱率乘以每天每系统为模拟4.38E-06的扰乱率或4375FIT。这意味着,如果同一供应商在50万辆车中采用基于1百万门SRAMFPGA的安全系统,把扰乱数1.05E-4乘以路上的车辆/系统的数量,就得到所有车辆每天有52.5的总扰乱数(假设车辆做恒速工作)。

这就相当于每27.4分钟出现 扰乱。即使对于每天两小时的中等车辆使用率,仍然有每天两次扰乱。因为这些都是稳故障,它们都将持续下去,直到SRAMFPGA被二次加载(通常要重新上电或强迫配置)。

在目前的半导体技术中,器件中的软错误已经受到高度关注。随着器件尺寸持续缩小,人们广泛认为这些软错误将成为主要问题。这些错误可能常常极大地降低系统的可用性。为了把系统的可用性维持在可以接受的水平,人们强烈要求避免出现软错误。

未来要做的工作

当选择FPGA的时候,至关重要的是评价每一种可编程架构所有权的总成本,并识别具有本质上可靠的内核技术的供应商,不要采用为低档次要求应用而设计的二等品质的商用产品。

对于采用SRAMFPGA的设计工程师来说,有必要实现检测和校正配置错误的电路,尽管这会增加系统成本和复杂性。此外,辐射测试数据表明,反融丝和基于闪存的FPGA不易于出现因中子导致的扰乱而造成的配置丢失。这使它们特别适用于可靠性要求高的应用。

现在,想象以下稍微不同的外景:你以每小时75英里的速度驾驶着新的2006车型在高速公路奔驰,耳畔聆听着优美的SteveMiller的GreatestHits乐曲。由于对引擎管理系统中采用的基于非易失性闪存的FPGA充满信心,你推杆加速狂飙,体验着极速带来的快乐,享受着舒适和无故障的旅行。

Copyright © 2018-2020 PbootCMS All Rights Reserved. 粤ICP备18049383号

XML地图